- 品牌

- 京晓设计

- 服务内容

- 技术开发

- 版本类型

- 普通版

PCB打样PCB的中文名称为印制电路板又称印刷电路板、印刷线路板是重要的电子部件是电子元器件的支撑体?是电子元器件电气连接的提供者。由于它是采用电子印刷术制作的故被称为“印刷”电路板。PCB打样就是指印制电路板在批量生产前的试产主要应用为电子工程师在设计好电路?并完成PCBLayout之后向工厂进行小批量试产的过程即为PCB打样。而PCB打样的生产数量一般没有具体界线一般是工程师在产品设计未完成确认和完成测试之前都称之为PCB打样。PCB设计中等长线处理方式技巧有哪些?恩施设计PCB设计教程

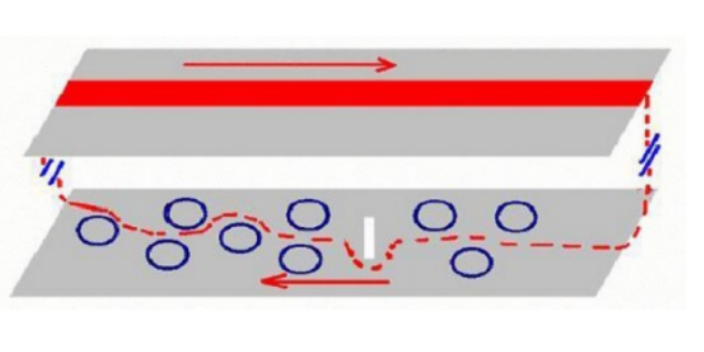

单面板单面板(Single-SidedBoards)在基本的PCB上,零件集中在其中一面,导线则集中在另一面上。因为导线只出现在其中一面,所以这种PCB叫作单面板(Single-sided)。因为单面板在设计线路上有许多严格的限制(因为只有一面,布线间不能交叉而必须绕独自的路径),所以只有早期的电路才使用这类的板子。双面板双面板(Double-SidedBoards)这种电路板的两面都有布线,不过要用上两面的导线,必须要在两面间有适当的电路连接才行。这种电路间的“桥梁”叫做导孔(via)。导孔是在PCB上,充满或涂上金属的小洞,它可以与两面的导线相连接。因为双面板的面积比单面板大了一倍,而且因为布线可以互相交错(可以绕到另一面),它更适合用在比单面板更复杂的电路上。恩施哪里的PCB设计布线屏蔽腔的设计具体步骤流程。

印制电路板的设计是以电路原理图为根据,实现电路设计者所需要的功能。印刷电路板的设计主要指版图设计,需要考虑外部连接的布局、内部电子元件的优化布局、金属连线和通孔的优化布局、电磁保护、热耗散等各种因素。的版图设计可以节约生产成本,达到良好的电路性能和散热性能。简单的版图设计可以用手工实现,复杂的版图设计需要借助计算机辅助设计(CAD)实现。根据电路层数分类:分为单面板、双面板和多层板。常见的多层板一般为4层板或6层板,复杂的多层板可达十几层。

在步骤s305中,统计所有绘制packagegeometry/pastemask层面的smdpin的坐标。在该实施例中,smdpin器件如果原本就带有pastemask(钢板),就不会额外自动绘制packagegeometry/pastemask层面,相反之,自动绘制packagegeometry/pastemask层面的smdpin即是遗漏pastemask(钢板)。在该实施例中,将统计得到的所有绘制在packagegeometry/pastemask层面的smdpin的坐标以列表的方式显示输出;其中,该处为excel列表的方式,当然也可以采用allegro格式,在此不再赘述。在本发明实施例中,当接收到在所述列表上对应的坐标的点击指令时,控制点亮与点击的坐标相对应的smdpin,即:布局工程师直接点击坐标,以便可快速搜寻到错误,并修正。图5示出了本发明提供的pcb设计中layout的检查系统的结构框图,为了便于说明,图中给出了与本发明实施例相关的部分。pcb设计中layout的检查系统包括:选项参数输入模块11,用于接收在预先配置的布局检查选项配置窗口上输入的检查选项和pinsize参数;层面绘制模块12,用于将smdpin中心点作为基准,根据输入的所述pinsize参数,以smdpin的半径+预设参数阈值为半径,绘制packagegeometry/pastemask层面;坐标获取模块13。 布线优化的工艺技巧有哪些?

按产业链上下游来分类,可以分为原材料-覆铜板-印刷电路板-电子产品应用,其关系简单表示为:福斯莱特电子产业链玻纤布:玻纤布是覆铜板的原材料之一,由玻纤纱纺织而成,约占覆铜板成本的40%(厚板)和25%(薄板)。玻纤纱由硅砂等原料在窑中煅烧成液态,通过极细小的合金喷嘴拉成极细玻纤,再将几百根玻纤缠绞成玻纤纱。窑的建设投资巨大,一般需上亿资金,且一旦点火必须24小时不间断生产,进入退出成本巨大。玻纤布制造则和织布企业类似,可以通过控制转速来控制产能及品质,且规格比较单一和稳定,自二战以来几乎没有规格上的太大变化。PCB设计的整体模块布局。黄冈如何PCB设计哪家好

在PCB设计中如何绘制结构特殊区域及拼板?恩施设计PCB设计教程

设计在不同阶段需要进行不同的设置,在布局阶段可以采用大格点进行器件布局;对于IC、非定位接插件等大器件,可以选用50~100mil的格点精度进行布局,而对于电阻电容和电感等无源小器件,可采用25mil的格点进行布局。大格点的精度有利于器件的对齐和布局的美观。在高速布线时,我们一般来用毫米mm为单位,我们大多采用米尔mil为单位。在通常情况下,所有的元件尽量布置在电路板的同一面上,只有当顶层元件过密时,才能将一些高度有限并且发热量小的器件,如贴片电阻、贴片电容、贴片芯片等放在底层。在保证电气性能的前提下,元件应放置在栅格上且相互平行或垂直排列,以求整齐、美观;元件排列要紧凑,元件在整个版面上应分布均匀、疏密一致。恩施设计PCB设计教程

布线阶段:信号完整性与电源稳定性走线规则阻抗匹配:高速信号(如DDR、USB 3.0)需严格匹配阻抗(如50Ω/90Ω),避免反射。串扰控制:平行走线间距≥3倍线宽,敏感信号(如模拟信号)需包地处理。45°拐角:高速信号避免直角拐弯,采用45°或圆弧走线减少阻抗突变。电源与地设计去耦电容布局:在芯片电源引脚附近(<5mm)放置0.1μF+10μF组合电容,缩短回流路径。电源平面分割:模拟/数字电源需**分割,高频信号需完整地平面作为参考。关键信号处理差分对:等长误差<5mil,组内间距保持恒定,避免跨分割。时钟信号:采用包地处理,远离大电流路径和I/O接口。专业 PCB 设计,保障电路安全。鄂...

- 咸宁PCB设计销售电话 2025-06-14

- 高效PCB设计布线 2025-06-14

- 湖北了解PCB设计规范 2025-06-14

- 襄阳专业PCB设计怎么样 2025-06-14

- 随州如何PCB设计销售 2025-06-14

- 鄂州哪里的PCB设计 2025-06-14

- 襄阳哪里的PCB设计批发 2025-06-14

- 湖北了解PCB设计加工 2025-06-14

- 设计PCB设计原理 2025-06-14

- 湖北常规PCB设计销售电话 2025-06-14

- 咸宁定制PCB设计走线 2025-06-12

- 武汉专业PCB设计功能 2025-06-12

- 宜昌常规PCB设计包括哪些 2025-06-12

- 荆门正规PCB设计布局 2025-06-12

- 黄冈了解PCB设计批发 2025-06-12

- 鄂州打造PCB设计 2025-06-12

- 十堰正规PCB制版多少钱 06-16

- 黄石高速PCB制版功能 06-16

- 宜昌正规PCB制版走线 06-16

- 孝感设计PCB制版批发 06-16

- 荆门打造PCB制版布线 06-16

- 常规PCB培训功能 06-16

- 专业PCB培训批发 06-16

- 荆门定制PCB制版哪家好 06-16

- 深圳常规PCB培训厂家 06-15

- 武汉定制PCB培训销售电话 06-15