- 品牌

- 京晓设计

- 服务内容

- 技术开发

- 版本类型

- 普通版

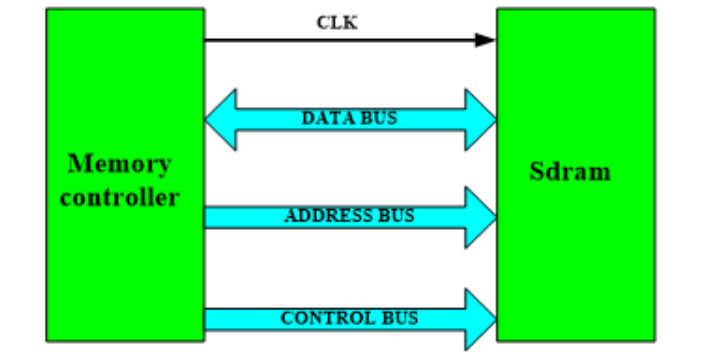

SDRAM模块SDRAM介绍:SDRAM是SynchronousDynamicRandomAccessMemory(同步动态随机存储器)的简称,是使用很的一种存储器,一般应用在200MHz以下,常用在33MHz、90MHz、100MHz、125MHz、133MHz等。其中同步是指时钟频率与SDRAM控制器如CPU前端其时钟频率与CPU前端总线的系统时钟频率相同,并且内部命令的发送和数据的传输都以它为准;动态是指存储阵列需要不断刷新来保证数据不丢失;随机是指数据不是线性一次存储,而是自由指定地址进行数据的读写。为了配合SDRAM控制芯片的总线位宽,必须配合适当数量的SDRAM芯片颗粒,如32位的CPU芯片,如果用位宽16bit的SDRAM芯片就需要2片,而位宽8bit的SDRAM芯片则就需要4片。是某厂家的SDRAM芯片封装示意图,图中列出了16bit、8bit、4bit不同位宽的信号网络管脚分配情况以及信号网络说明。PCB设计中如何评估平面层数?恩施如何PCB设计报价

工艺、层叠和阻抗信息确认(1)与客户确认阻抗类型,常见阻抗类型如下:常规阻抗:单端50欧姆,差分100欧姆。特殊阻抗:射频线单端50欧姆、75欧姆隔层参考,USB接口差分90欧姆,RS485串口差分120欧姆。(2)传递《PCBLayout业务资料及要求》中的工艺要求、层叠排布信息和阻抗要求至工艺工程师,由工艺工程师生成《PCB加工工艺要求说明书》,基于以下几点进行说明:信号层夹在电源层和地层之间时,信号层靠近地层。差分间距≤2倍线宽。相邻信号层间距拉大。阻抗线所在的层号。(3)检查《PCB加工工艺要求说明书》信息是否有遗漏,错误,核对无误后再与客户进行确认。荆门如何PCB设计加工PCB布局布线设计规则。

ADC/DAC电路:(2)模拟地与数字地处理:大多数ADC、DAC往往依据数据手册和提供的参考设计进行地分割处理,通常情况是将PCB地层分为模拟地AGND和数字地DGND,然后将二者单点连接,(3)模拟电源和数字电源当电源入口只有统一的数字地和数字电源时,在电源入口处通过将数字地加磁珠或电感,将数字地拆分成成模拟地;同样在电源入口处将数字电源通过磁珠或电感拆分成模拟电源。负载端所有的数字电源都通过入口处数字电源生成、模拟电源都通过经过磁珠或电感隔离后的模拟电源生成。如果在电源入口处(外部提供的电源)既有模拟地又有数字地、既有模拟电源又有数字电源,板子上所有的数字电源都用入口处的数字电源生成、模拟电源都用入口处的模拟电源生成。ADC和DAC器件的模拟电源一般采用LDO进行供电,因为其电流小、纹波小,而DC/DC会引入较大开关电源噪声,严重影响ADC/DAC器件性能,因此,模拟电路应该采用LDO进行供电。

存储模块介绍:存储器分类在我们的设计用到的存储器有SRAM、DRAM、EEPROM、Flash等,其中DDR系列用的是多的,其DDR-DDR4的详细参数如下:DDR采用TSSOP封装技术,而DDR2和DDR3内存均采用FBGA封装技术。TSSOP封装的外形尺寸较大,呈长方形,其优点是成本低、工艺要求不高,缺点是传导效果差,容易受干扰,散热不理想,而FBGA内存颗粒精致小巧,体积大约只有DDR内存颗粒的三分之一,有效地缩短信号传输距离,在抗干扰、散热等方面更有优势,而DDR4采用3DS(3-DimensionalStack)三维堆叠技术来增大单颗芯片容量,封装外形则与DDR2、DDR3差别不大。制造工艺不断提高,从DDR到DDR2再到DDR3内存,其制造工艺都在不断改善,更高工艺水平会使内存电气性能更好,成本更低;DDR内存颗粒大范围采用0.13微米制造工艺,而DDR2采用了0.09微米制造工艺,DDR3则采用了全新65nm制造工艺,而DDR4使用20nm以下的工艺来制造,从DDR~DDR4的具体参数如下表所示。DDR与SDRAM信号的不同之处在哪?

SDRAM各管脚功能说明:1、CLK是由系统时钟驱动的,SDRAM所有的输入信号都是在CLK的上升沿采样,CLK还用于触发内部计数器和输出寄存器;2、CKE为时钟使能信号,高电平时时钟有效,低电平时时钟无效,CKE为低电平时SDRAM处于预充电断电模式和自刷新模式。此时包括CLK在内的所有输入Buffer都被禁用,以降低功耗,CKE可以直接接高电平。3、CS#为片选信号,低电平有效,当CS#为高时器件内部所有的命令信号都被屏蔽,同时,CS#也是命令信号的一部分。4、RAS#、CAS#、WE#分别为行选择、列选择、写使能信号,低电平有效,这三个信号与CS#一起组合定义输入的命令。5、DQML,DQMU为数据掩码信号。写数据时,当DQM为高电平时对应的写入数据无效,DQML与DQMU分别对应于数据信号的低8位与高8位。6、A<0..12>为地址总线信号,在读写命令时行列地址都由该总线输入。7、BA0、BA1为BANK地址信号,用以确定当前的命令操作对哪一个BANK有效。8、DQ<0..15>为数据总线信号,读写操作时的数据信号通过该总线输出或输入。PCB设置中PCI-E板卡设计要求是什么?十堰正规PCB设计规范

不同存储容量及不同数据宽度的器件有所不同。恩施如何PCB设计报价

DDR与SDRAM信号的不同之处,1、DDR的数据信号与地址\控制信号是参考不同的时钟信号,数据信号参考DQS选通信号,地址\控制信号参考CK\CK#差分时钟信号;而SDRAM信号的数据、地址、控制信号是参考同一个时钟信号。2、数据信号参考的时钟信号即DQS信号是上升沿和下降沿都有效,即DQS信号的上升沿和下降沿都可以触发和锁存数据,而SDRAM的时钟信号只有在上升沿有效,相对而言DDR的数据速率翻倍。3、DDR的数据信号通常分成几组,如每8位数据信号加一位选通信号DQS组成一组,同一组的数据信号参考相同组里的选通信号。4、为DDRSDRAM接口同步工作示意图,数据信号与选通信号分成多组,同组内的数据信号参考同组内的选通信号;地址、控制信号参考CK\CK#差分时钟信号。恩施如何PCB设计报价

武汉京晓科技有限公司汇集了大量的优秀人才,集企业奇思,创经济奇迹,一群有梦想有朝气的团队不断在前进的道路上开创新天地,绘画新蓝图,在湖北省等地区的电工电气中始终保持良好的信誉,信奉着“争取每一个客户不容易,失去每一个用户很简单”的理念,市场是企业的方向,质量是企业的生命,在公司有效方针的领导下,全体上下,团结一致,共同进退,齐心协力把各方面工作做得更好,努力开创工作的新局面,公司的新高度,未来武汉京晓科技供应和您一起奔向更美好的未来,即使现在有一点小小的成绩,也不足以骄傲,过去的种种都已成为昨日我们只有总结经验,才能继续上路,让我们一起点燃新的希望,放飞新的梦想!

工具推荐原理图与Layout:Altium Designer、Cadence Allegro、Mentor PADS。仿真验证:ANSYS SIwave(信号完整性)、HyperLynx(电源完整性)、CST(EMC)。协同设计:Allegro、Upverter(云端协作)。五、结语PCB Layout是一门融合了电磁学、材料学和工程美学的综合技术。在5G、AI、新能源汽车等领域的驱动下,工程师需不断更新知识体系,掌握高频高速设计方法,同时借助仿真工具和自动化流程提升效率。未来,PCB设计将进一步向“小型化、高性能、绿色化”方向发展,成为电子创新的核心竞争力之一。以下是PCB Layout相关...

- 随州专业PCB设计走线 2025-07-14

- 湖北定制PCB设计怎么样 2025-07-14

- 襄阳哪里的PCB设计报价 2025-07-14

- 鄂州设计PCB设计规范 2025-07-14

- 如何PCB设计多少钱 2025-07-13

- 荆门设计PCB设计报价 2025-07-13

- 黄冈哪里的PCB设计 2025-07-13

- 荆州专业PCB设计布线 2025-07-13

- 定制PCB设计多少钱 2025-07-13

- 随州什么是PCB设计 2025-07-13

- 十堰如何PCB设计批发 2025-07-12

- 荆门什么是PCB设计怎么样 2025-07-12

- 恩施打造PCB设计原理 2025-07-12

- 荆门高速PCB设计报价 2025-07-11

- 恩施常规PCB设计多少钱 2025-07-11

- 孝感设计PCB设计销售电话 2025-07-11

- 孝感印制PCB制板销售 07-14

- 孝感高速PCB制版 07-14

- 鄂州正规PCB制版厂家 07-14

- 湖北定制PCB设计怎么样 07-14

- 襄阳哪里的PCB设计报价 07-14

- 深圳正规PCB培训批发 07-14

- 鄂州设计PCB设计规范 07-14

- 襄阳焊接PCB制板价格大全 07-13

- 如何PCB设计多少钱 07-13

- 武汉印制PCB制板批发 07-13