- 品牌

- 京晓设计

- 服务内容

- 技术开发

- 版本类型

- 普通版

统计所有绘制packagegeometry/pastemask层面的smdpin的坐标。作为一种改进的方案,当在所述布局检查选项配置窗口上选择所述report选项时,所述方法还包括下述步骤:将统计得到的所有绘制在packagegeometry/pastemask层面的smdpin的坐标以列表的方式显示输出。作为一种改进的方案,所述方法还包括下述步骤:当接收到在所述列表上对对应的坐标的点击指令时,控制点亮与点击的坐标相对应的smdpin。本发明的另一目的在于提供一种pcb设计中layout的检查系统,所述系统包括:选项参数输入模块,用于接收在预先配置的布局检查选项配置窗口上输入的检查选项和pinsize参数;层面绘制模块,用于将smdpin中心点作为基准,根据输入的所述pinsize参数,以smdpin的半径+预设参数阈值为半径,绘制packagegeometry/pastemask层面;坐标获取模块,用于获取绘制得到的所述packagegeometry/pastemask层面上所有smdpin的坐标。作为一种改进的方案,所述选项参数输入模块具体包括:布局检查选项配置窗口调用模块,用于当接收到输入的布局检查指令时,控制调用并显示预先配置的布局检查选项配置窗口;命令接收模块,用于接收在所述布局检查选项配置窗口上输入的pintype选择指令以及操作选项命令。 PCB设计是一个充满挑战与机遇的领域。武汉了解PCB设计布线

3、在高速PCB设计中,如何解决信号的完整性问题?信号完整性基本上是阻抗匹配的问题。而影响阻抗匹配的因素有信号源的架构和输出阻抗(outputimpedance),走线的特性阻抗,负载端的特性,走线的拓朴(topology)架构等。解决的方式是靠端接(termination)与调整走线的拓朴。4、差分信号线中间可否加地线?差分信号中间一般是不能加地线。因为差分信号的应用原理重要的一点便是利用差分信号间相互耦合(coupling)所带来的好处,如fluxcancellation,抗噪声(noiseimmunity)能力等。若在中间加地线,便会破坏耦合效应。5、在布时钟时,有必要两边加地线屏蔽吗?是否加屏蔽地线要根据板上的串扰/EMI情况来决定,而且如对屏蔽地线的处理不好,有可能反而会使情况更糟。6、allegro布线时出现一截一截的线段(有个小方框)如何处理?出现这个的原因是模块复用后,自动产生了一个自动命名的group,所以解决这个问题的关键就是重新打散这个group,在placementedit状态下选择group然后打散即可。完成这个命令后,移动所有小框的走线敲击ix00坐标即可。黄冈了解PCB设计批发这些参数影响信号在PCB上的传输速度和衰减情况,特别是在高频电路设计中尤为重要。

质量控制是PCB设计流程的重要组成部分,一般的质量控制手段包括:设计自检、设计互检、评审会议、专项检查等。原理图和结构要素图是基本的设放置顺序。放置与结构有紧密配合的元器件,如电源插座、指示灯、开关、连接器等。放置特殊元器件,如大的元器件、重的元器件、发热元器件、变压器、IC等。放置小的元器件。计要求,网络DRC检查和结构检查就是分别确认PCB设计满足原理图网表和结构要素图两项输入条件。电路板尺寸和CAD图纸要求加工尺寸是否相符合。

7、如何尽可能的达到EMC要求,又不致造成太大的成本压力?PCB板上会因EMC而增加的成本通常是因增加地层数目以增强屏蔽效应及增加了ferritebead、choke等抑制高频谐波器件的缘故。除此之外,通常还是需搭配其它机构上的屏蔽结构才能使整个系统通过EMC的要求。以下就PCB板的设计技巧提供几个降低电路产生的电磁辐射效应:尽可能选用信号斜率(slewrate)较慢的器件,以降低信号所产生的高频成分。注意高频器件摆放的位置,不要太靠近对外的连接器。创新 PCB 设计,突破技术瓶颈。

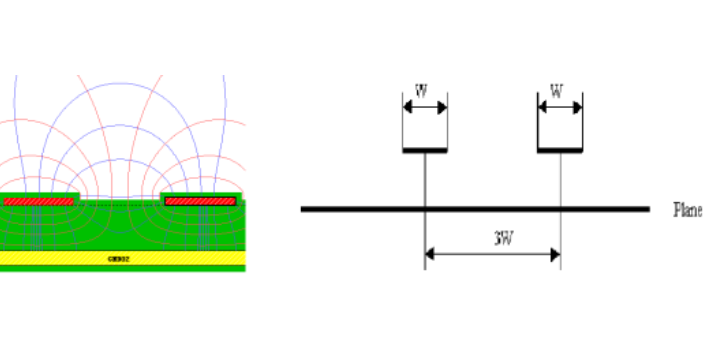

PCB设计是指打印电路板(Printed Circuit Board)的设计,这是电子产品制造过程中不可缺少的一个环节。在PCB设计中,通过将电路图上的电子元器件布局设计在板子上,再使用PCB设计软件进行连线、走线、填充等操作,终形成一张电路板,将电子元器件连接起来,使整个电路系统能够正常工作。 PCB设计的质量和精度对电子产品的性能和稳定性有很大的影响,因此需要由专业的电路工程师进行设计和检验。射频:是电磁波按应用划分的定义,专指具有一定波长可用于无线电通信的电磁波,射频PCB可以定义为具有频率在30MHz至6GHz范围模拟信号的PCB。2、微带线:是一种传输线类型。由平行而不相交的带状导体和接地平面构成。所示它是由导体条带(在基片的一边)和接地板(在基片的另一边)所构成的传输线。微带线是由介质基片,接地平板和导体条带三部分组成。信赖的 PCB 设计,树立良好口碑。十堰正规PCB设计布局

我们的PCB设计能够提高您的产品差异化。武汉了解PCB设计布线

布线优化的步骤,连通性检查-DRC检查-STUB残端走线检查-跨分割走线检查-走线窜扰检查-残铜率检查-走线角度检查。连通性检查:整版连通为100%,未连接网络需确认并记录。整版DRC检查:对整版DRC进行检查、修改、确认、记录。STUB残端走线及过孔检查:整版检查整版STUB残端走线及孤立过孔并删除。跨分割区域检查:检查所有分隔带区域,并对在分隔带上的阻抗线进行调整。走线串扰检查:所有相邻层走线检查并调整。残铜率检查:对称层需检查残铜率是否对称并进行调整。走线角度检查:检查整版直角、锐角走线。武汉了解PCB设计布线

工具推荐原理图与Layout:Altium Designer、Cadence Allegro、Mentor PADS。仿真验证:ANSYS SIwave(信号完整性)、HyperLynx(电源完整性)、CST(EMC)。协同设计:Allegro、Upverter(云端协作)。五、结语PCB Layout是一门融合了电磁学、材料学和工程美学的综合技术。在5G、AI、新能源汽车等领域的驱动下,工程师需不断更新知识体系,掌握高频高速设计方法,同时借助仿真工具和自动化流程提升效率。未来,PCB设计将进一步向“小型化、高性能、绿色化”方向发展,成为电子创新的核心竞争力之一。以下是PCB Layout相关...

- 黄冈哪里的PCB设计 2025-06-20

- 咸宁高效PCB设计厂家 2025-06-20

- 荆门设计PCB设计布线 2025-06-19

- 鄂州正规PCB设计销售 2025-06-19

- 襄阳定制PCB设计原理 2025-06-19

- 鄂州如何PCB设计功能 2025-06-19

- 孝感什么是PCB设计教程 2025-06-18

- 荆门定制PCB设计教程 2025-06-18

- 荆州如何PCB设计销售电话 2025-06-18

- 黄冈专业PCB设计多少钱 2025-06-18

- 鄂州专业PCB设计布线 2025-06-14

- 咸宁PCB设计销售电话 2025-06-14

- 高效PCB设计布线 2025-06-14

- 湖北了解PCB设计规范 2025-06-14

- 襄阳专业PCB设计怎么样 2025-06-14

- 随州如何PCB设计销售 2025-06-14

- 武汉定制PCB制板包括哪些 06-19

- 黄冈印制PCB制板加工 06-19

- 黄石定制PCB制板加工 06-19

- 随州焊接PCB制板功能 06-19

- 鄂州正规PCB设计销售 06-19

- 襄阳定制PCB设计原理 06-19

- 黄冈专业PCB制板走线 06-19

- 鄂州如何PCB设计功能 06-19

- 黄石高速PCB制板厂家 06-19

- 湖北定制PCB制板价格大全 06-19